|

|

|

|

Selecting the right hardware for Reverse Time Migration |

As mentioned above, current FPGAs have the resources to implement hundreds of floating-point arithmetic units. Therefore, one stencil operator design only consumes a small portion of the total resources of an FPGA. To make a full utilization of all the resources on an FPGA, one straightforward way is to fill multiple stencil operators into one FPGA.

However, increasing the number of stencil operators does not always improve the overall performance due to the constraint of the memory bandwidth between the FPGA and the onboard memories. When the input streams for the multiple stencil operators approach the saturation point of the memory bandwidth, increasing the number of stencil operators may not improve the performance any more.

Instead of implementing multiple stencil operators, another strategy is to extend the

streaming pass to process multiple time steps. In RTM, the ![]() of modelling

is a fraction of the sampling of the recorded data. These wavefields are

intermediate results unneeded in the imaging process.

The streaming architecture of FPGA

provides an ideal platform for convolving multiple time steps in one pass.

of modelling

is a fraction of the sampling of the recorded data. These wavefields are

intermediate results unneeded in the imaging process.

The streaming architecture of FPGA

provides an ideal platform for convolving multiple time steps in one pass.

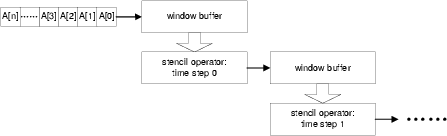

As mentioned in the previous sections, as long as the FPGA has enough resources, we can add more computation units without reducing the throughput of the design. Therefore, instead of sending the results of the stencil operator to the output port, we can push the results into another stencil operator and perform the computation for the next time step.

Figure 8 shows the general structure for processing multiple time steps in one pass. As mentioned in previous section, at the input port, a window buffer is used to store all the data items needed for the stencil operator. Similarly, we can put another window buffer to store the convolution results of time step ![]() and feed the corresponding values into the stencil operator for time step

and feed the corresponding values into the stencil operator for time step ![]() . Therefore, we can multiply the computation performance without consuming multiple times of memory bandwidth.

. Therefore, we can multiply the computation performance without consuming multiple times of memory bandwidth.

|

|---|

|

multiple-time-step

Figure 8. General structure for processing multiple time steps in one pass.[NR] |

|

|

|

|

|

|

Selecting the right hardware for Reverse Time Migration |